## **POPULAR DEMOCRATIC REPUBLIC OF ALGERIA** HIGHER EDUCATION AND SCIENTIFIC RESEARCH'SMINISTRY

## University KASDI MERBAH OUARGLA

Faculty of new information technologies and communication Department of computer and information technology

LMD Master 2018/2019 Option:

Dissertation

For the Master degree in network administration and security **Title:**

# Solving Task Migration Problems by Optimizing the Crossover and Mutation probabilities using tabu search

Presented in : 02 / 07 / 2019

**Presented by:** . Benazia Meriem

Kemassi Imane

## Jury members:

Dr.Chrite Abd El Hakim

Dr. Djediai Hemida

Dr. Belekbir Djalila

Université KASDI MERBAH OUARGLA Examiner

Université KASDI MERBAH OUARGLA

President

Université KASDI MERBAH OUARGLA Directed

Academic Year 2018-2019

# ABSTRACT

-----

-----

Task migration (TM) is the act of transferring a process between two processing units, it is considered as an effective strategy to achieve load balancing and higher source utilization, in another way, it is a call to the operating system during run time.TM has been widely used in the distributed systems domain, but as a drawback, the migration time overhead may be long in point that it will increase network congestion and degrade the system performance, we aim to optimize those problems by using genetic algorithms (GA).

Tabu search is a metaheuristic that guides a local search heuristic to escape from local minima and in the same time, to implement an exploration scheme. The simple tabu search algorithm applies a local search where at each iteration, the best solution among the list of neighborhoods is selected and remarked as a new current solution. A short-term memory is implemented as a tabu list where solution attributes are stored to avoid short term cycling.

Crossover is the process in which genes are selected from the parent chromosomes and new offspring is created, where the mutation is applied on one chromosome. The genetic algorithms' performance is largely influenced by crossover and mutation operators, the probabilities of applying those operators can be optimized by tabu search technique probabilities.

#### **Keywords:**

Task migration, Embedded Systems, Genetic algorithms, tabu search, crossover and mutation probabilities.

#### ملخص

ترحيل المهام هو نقل عملية بين وحدتي معالجة، و بتعريف آخر هو استدعاء لنظام التشغيل أثناء وقت التشغيل و أستخدم على نطاق واسع في مجال الأنظمة الموزعة ،برغم من هذه المحاسن إلا أن العيب فيها يكمن في طول وقت الترحيل مما يتسبب في زيادة ازدحام الشبكة و تقليل من أداء النظام. نحن نهدف إلى تحسين هذه المشاكل باستخدام الخوار زميات الجينية.

البحث في علامة تبويب هو إجراء عالي المستوى مصمما لإيجاد أو تحديد مجريات الأمور التي قد توفر حلا جيدا للتحسين ، بحيث تطبق خوارزمية البسيطة للبحث في علامة تبويب بحثا محليا في كل عملية تكرارية لتحديد أفضل حل ضمن قائمة تبويب و تعيينه كحل جديد ،وتعرف قائمة التبويب بأنها عبارة عن ذاكرة قصيرة المدى حيث يتم تخزين كروموسومات فيها.

يتأثر أداء خوارزميات الجينية إلى حد كبير بعملتي التبديل و التحويل. حيث أن التبديل هو عملية اختيار الجينات من الكروموسومات الأصل و إنشاء كروموسوم جديد، و يتم تطبيق التحويل على جيني واحد و تحسن احتمالات تطبيق التبديل و التحويل من خلال تحسين احتمالات البحث في التبويب.

#### الكلمات المفتاحية:

ترحيل المهام ، الأنظمة المدمجة ، الخوار زميات الجينية ، البحث عن علامة تبويب ، احتمالات التبادل والتحويل.

# Table of content

| Abs  | tract     |                                             | <u>I</u> |

|------|-----------|---------------------------------------------|----------|

| فص   | م         |                                             | II       |

| Tab  | le of co  | ntent                                       | III      |

| Figu | ures list |                                             | IX       |

| Tab  | les list. |                                             | XII      |

| Gen  | eral int  | roduction                                   | 1        |

| 1.   | Proble    | m definition                                | 1        |

| 2.   | Contri    | butions                                     | 2        |

| 3.   | Thesis    | Overview                                    | 3        |

| Cha  | pter 1    | Network on chip                             | 4        |

| 1.   | Introd    | uction                                      | 4        |

| 2.   | Embeo     | lded System                                 | 5        |

| 2.1  | Embe      | edded System Definition                     | 5        |

| 2.2  | Real-     | Time System:                                | 5        |

|      | 2.2.1     | Real-Time Scheduling                        | 5        |

|      | 2.2       | .1.1 Rate Monotonic (RM)                    | 5        |

|      | 2.2       | .1.2 Deadlock Monotonic (DM)                | 7        |

| 2.3  | Embe      | edded System Different Architectures        | 7        |

|      | 2.3.1     | System on Chip (SoC)                        | 7        |

|      | 2.3.2     | Multiprocessor System-On-Chip (MPSOC)       | 8        |

|      | 2.3.3     | NoC                                         | 8        |

|      | 2.3.4     | Comparison of Embedded System Architectures | 8        |

| 3.   | NoC N     | Iain Components                             | 9        |

| 3.1  | NoC       | Layered Communication                       | 9        |

|      | 3.1.1     | The Network Layer                           | 10       |

|      | 3.1.2     | The Data Link Layer                         | .10      |

|      | 3.1.3     | The physical layer                          | 10       |

| 3.2  | NoC       | Main Components:                            | 11       |

|      | 3.2.1     | Node                                        | .11      |

|      | 3.2.2     | The Resource-Network Interface (RNI)        | 11       |

|     | 3.2.3 | Router                                            | 12 |

|-----|-------|---------------------------------------------------|----|

|     | 3.2.4 | The links                                         | 13 |

| 3.3 | Flov  | v control:                                        | 14 |

|     | 3.3.1 | The delay of the packets                          | 14 |

|     | a.    | The size of queues                                | 14 |

|     | b.    | The position of the queues                        | 14 |

|     |       | i. Input queues                                   | 14 |

|     |       | ii. Output queues                                 | 15 |

|     |       | iii. Queues in virtual output or virtual channels | 15 |

|     | 3.3.2 | The switching matrix:                             | 15 |

|     | 3.3.3 | Arbitration                                       | 15 |

|     |       | i. By TDMA                                        | 16 |

|     |       | ii. By time-slot reservation                      | 16 |

|     |       | iii. By tourniquet or round-robin                 | 16 |

|     |       | iiii. By fixed priority                           | 16 |

| 3.4 | NoC   | Main Characteristics:                             | 16 |

|     | 3.4.1 | Topology:                                         | 16 |

|     |       | 3.4.1.1 Mesh Topology                             | 17 |

|     |       | 3.4.1.2 Torus Topology                            | 17 |

|     |       | 3.4.1.3 Ring topology                             | 17 |

|     |       | 3.4.1.4 Star Topology                             | 18 |

|     |       | 3.4.1.5 Binary tree topology                      | 18 |

|     |       | 3.4.1.6 Fat binary tree topology                  | 18 |

|     |       | 3.4.1.7 Butterfly topology                        | 19 |

|     |       | 3.4.1.8 Spin topology                             | 19 |

|     | 3.4.2 | Switching Protocol                                | 19 |

|     |       | 3.4.2.1 Circuit Switching                         | 19 |

|     |       | 3.4.2.2 Packet Switching                          | 20 |

|     |       | a. Store and Forward (SAF)                        | 20 |

|     |       | b. Virtual Cut-Through (VCT) Switching            | 21 |

|     |       | c. Wormhole Switching                             | 22 |

|     | 3.4.3 | Routing Protocol:                                 | 22 |

|                                                                                                                                          | 3.4.3.1 Deterministic Routing Algorithms                                                                                                                                                                                                                                                                                             | 24                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                                                                                                          | a. Shortest Path Routing                                                                                                                                                                                                                                                                                                             | 24                                                                                     |

|                                                                                                                                          | i. Distance Vector Routing                                                                                                                                                                                                                                                                                                           | 24                                                                                     |

|                                                                                                                                          | ii. Link State Routing                                                                                                                                                                                                                                                                                                               | 25                                                                                     |

|                                                                                                                                          | b. Source Routing                                                                                                                                                                                                                                                                                                                    | 25                                                                                     |

|                                                                                                                                          | c. Destination-tag Routing                                                                                                                                                                                                                                                                                                           | 25                                                                                     |

|                                                                                                                                          | d. Topology Adaptive Routing                                                                                                                                                                                                                                                                                                         | 26                                                                                     |

|                                                                                                                                          | 3.4.3.2 Adaptive Routing Algorithms                                                                                                                                                                                                                                                                                                  | 26                                                                                     |

|                                                                                                                                          | 3.4.3.3 Minimal Adaptive Routing                                                                                                                                                                                                                                                                                                     | 26                                                                                     |

|                                                                                                                                          | 3.4.3.4 Non-Minimal Adaptive Routing                                                                                                                                                                                                                                                                                                 | 27                                                                                     |

|                                                                                                                                          | 3.4.3.5 Turn Model                                                                                                                                                                                                                                                                                                                   | 28                                                                                     |

|                                                                                                                                          | 3.4.3.6 Randomized Routing Algorithms                                                                                                                                                                                                                                                                                                | 29                                                                                     |

|                                                                                                                                          | 3.4.3.7 Comparison of Routing Algorithms                                                                                                                                                                                                                                                                                             | 30                                                                                     |

| 4.                                                                                                                                       | Conclusion                                                                                                                                                                                                                                                                                                                           | 31                                                                                     |

| Cita                                                                                                                                     | apter 2: ENERGY EFFICIENCY AND DELAY MODEL                                                                                                                                                                                                                                                                                           |                                                                                        |

|                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

| 1.                                                                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                         | 32                                                                                     |

| 1.<br>2.                                                                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                      | 32                                                                                     |

| 2.                                                                                                                                       | Synchronous data flow                                                                                                                                                                                                                                                                                                                | 32                                                                                     |

| 2.<br>2.1                                                                                                                                | Synchronous data flow<br>Definition<br>Model structure                                                                                                                                                                                                                                                                               | 32<br>32<br>33                                                                         |

| 2.<br>2.1<br>2.2                                                                                                                         | Synchronous data flow<br>Definition<br>Model structure                                                                                                                                                                                                                                                                               | 32<br>32<br>33<br>34                                                                   |

| 2.<br>2.1<br>2.2                                                                                                                         | Synchronous data flow<br>Definition<br>Model structure<br>Scheduling policies over SDF                                                                                                                                                                                                                                               | 32<br>32<br>33<br>34<br>36                                                             |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> </ol>                                                                                        | Synchronous data flow.         Definition.         Model structure.         Scheduling policies over SDF.         2.3.1Scheduling Strategies.                                                                                                                                                                                        | 32<br>32<br>33<br>34<br>36<br>37                                                       |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> </ol>                                                                            | Synchronous data flow<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.                                                                                                                                                                             | 32<br>32<br>33<br>34<br>36<br>37<br>37                                                 |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> <li>3.1</li> </ol>                                                               | Synchronous data flow<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.<br>Noc latency.                                                                                                                                                             | 32<br>32<br>33<br>34<br>36<br>37<br>37<br>37                                           |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> <li>3.1</li> <li>3.2</li> </ol>                                                  | Synchronous data flow.<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.<br>Noc latency.<br>Computation delay.                                                                                                                                      | 32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37                                     |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ol>                                     | Synchronous data flow.<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.<br>Noc latency.<br>Computation delay.                                                                                                                                      | 32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>37                               |

| <ol> <li>2.</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>4.</li> <li>5.</li> </ol> | Synchronous data flow.<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.<br>Noc latency.<br>Computation delay.<br>The communication delay.<br>Network on chip power model.                                                                          | 32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>37<br>37<br>37                   |

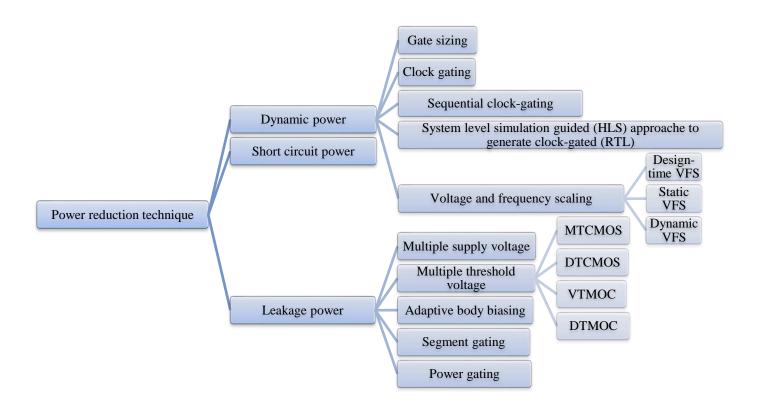

| <ol> <li>2.</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>4.</li> <li>5.</li> </ol> | Synchronous data flow.<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.<br>Noc latency.<br>Computation delay.<br>The communication delay.<br>Network on chip power model.<br>Power reduction techniques.                                           | 32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>37<br>37<br>37<br>39<br>39       |

| <ol> <li>2.</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3.</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>4.</li> <li>5.</li> </ol> | Synchronous data flow.<br>Definition.<br>Model structure.<br>Scheduling policies over SDF.<br>2.3.1Scheduling Strategies.<br>Network on chip delay model.<br>Noc latency.<br>Computation delay.<br>The communication delay.<br>Network on chip power model.<br>Power reduction techniques.<br>Techniques for reducing dynamic power. | 32<br>32<br>33<br>34<br>36<br>37<br>37<br>37<br>37<br>37<br>37<br>37<br>39<br>39<br>39 |

| 5.1.4 System level simulation guided (HLS) approach to generate clock-gated (RTL) | 41 |

|-----------------------------------------------------------------------------------|----|

| 5.1.5 Voltage and frequency scaling                                               | 42 |

| 5.2 Techniques for reducing short circuit power                                   | 45 |

| 5.3 Techniques for reducing leakage power                                         | 46 |

| 5.3.1 Multiple supply voltage                                                     | 46 |

| 5.3.2 Multiple threshold voltage                                                  | 48 |

| 5.3.3 Adaptive body biasing                                                       | 50 |

| 5.3.4 Power gating                                                                | 51 |

| 5.3.5 Segment gating                                                              | 52 |

| 6. Comparison between different power reduction techniques                        | 53 |

| 7. Conclusion.                                                                    | 54 |

## Chapter 3:HEURISTIC OPTIMIZATION ALGORITHMS BASED NETWORK ON CHIP......55

| 1.                                           | Introduction                                                                                                                                                                      | 55 |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2                                            | Preliminaries Of Heuristic Optimization Methods                                                                                                                                   | 56 |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>3. | Exhautive Search.<br>Local Search.<br>Divide and conquer.<br>Branch-and-Bound.<br>Dynamic programming.<br>Greedy Technique.<br>Characteristics Of Heuristic Optimization Methods. |    |

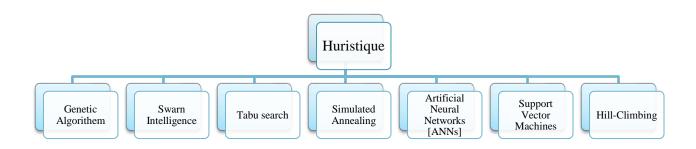

| 4.                                           | Classification Of Heuristic Optimization Methods                                                                                                                                  | 58 |

| 4.1                                          | Genetic Algorithms                                                                                                                                                                | 58 |

|                                              | 4.1.1 Definition                                                                                                                                                                  | 58 |

|                                              | 4.1.2 Working of Genetic Algorithm                                                                                                                                                | 58 |

|                                              | 4.1.3 Characteristics Of Genetic Algorithm                                                                                                                                        | 59 |

|                                              | 4.1.4 GA Operators                                                                                                                                                                |    |

|                                              | 4.1.4.1 The selection operation                                                                                                                                                   | 60 |

|                                              | 4.1.4.2 The crossover operation                                                                                                                                                   | 60 |

|                                              | 4.1.4.3 The Mutation Operation                                                                                                                                                    | 61 |

| 4.2                                          | Swarm Intelligence :                                                                                                                                                              | 61 |

|                                              | 4.2.1 The swarm algorithms                                                                                                                                                        | 62 |

| 4.3                                          | Tabu Search                                                                                                                                                                       | 62 |

| 4.4 | Simulated annealing (SA)                                 | 63 |

|-----|----------------------------------------------------------|----|

|     | 4.4.1 The SA algorithm                                   |    |

|     | 4.4.2 The simulated annealing algorithm                  | 63 |

| 4.5 | Neural Networks                                          | 63 |

| 4.6 | Artificial neural networks(ANNs)                         | 64 |

| 4.7 | Support Vector Machines (SVMs)                           | 64 |

| 4.8 | Hill-Climbing Algorithm                                  | 64 |

| 5.  | Mapping And Scheduling Techniques In Noc                 | 65 |

| 5.1 | Key Factors On Task Mapping:                             | 65 |

|     | 5.1.1 Target Architecture                                | 65 |

|     | 5.1.2 Abstraction Level Of The Application Specification | 65 |

|     | 5.1.3 Figures Of Merit                                   | 66 |

|     | 5.1.4 Common–Domain Semantic                             | 66 |

|     | 5.1.5 Topologies                                         | 66 |

|     | 5.1.6 Optimization Algorithms                            | 66 |

|     | 5.1.7 Tools                                              | 67 |

| 5.2 | Related Work Of Mapping And Scheduling Techniques In Noc |    |

| 6.  | Task Migration Mechanisms                                | 71 |

| 6.1 | Definition of task migration                             | 71 |

| 6.2 | Task Migration Mechanisms                                | 72 |

|     | 6.2.1 Checkpoints                                        | 72 |

|     | 6.2.2 debug registers                                    | 73 |

|     | 6.2.3 incoming migrations                                | 73 |

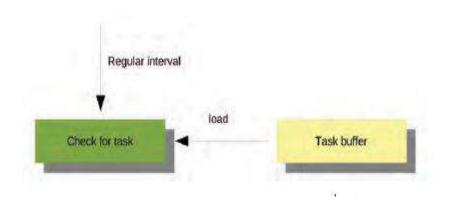

|     | 6.2.4 accepting task migrations by polling:              |    |

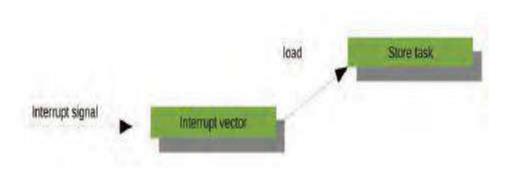

|     | 6.2.5 accepting task migrations by interrupts:           | 74 |

| 7.  | Conclusion                                               | 75 |

| CH  | IAPTER4: CONTRIBUTIONS, TESTS AND EXPERIMENT             | 76 |

| 1.  | Introduction                                             | 76 |

| 2.  | Contribution in task migration                           |    |

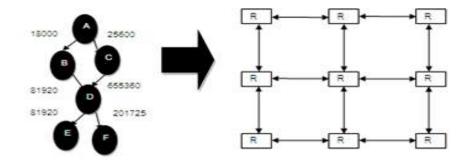

| 2.1 | Target architecture                                      | 77 |

Application......77

2.2

VII

| 2.3 | Task model                                                        | 77          |

|-----|-------------------------------------------------------------------|-------------|

| 2.4 | Benchmarks' multimedia applications (Case of study)               |             |

| 2.5 | Scheduling algorithm                                              | 80          |

| 2.6 | Routing algorithms                                                |             |

| 2.7 | Contribution in task migration                                    | 81          |

|     | 2.7.1 CPU stat                                                    | 81          |

|     | 2.7.2 Task stack                                                  |             |

|     | 2.7.3 Heap data                                                   |             |

|     | 2.7.4 Program code                                                | 82          |

|     | 2.7.5 Task associations                                           |             |

|     | 2.7.6 Global variables                                            |             |

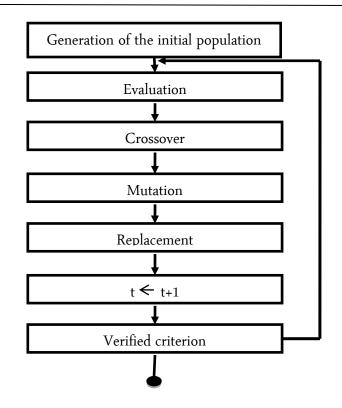

| 3.  | The use of genetic algorithms with task migration                 | 83          |

| 3.1 | Problem description                                               |             |

| 4.  | The use of genetic algorithms and tabu search with task migration | 87 <b>7</b> |

| 5.  | Experiments and case of studies                                   |             |

| 6.  | Conclusion                                                        | 101         |

| Ger | eral conclusion                                                   | 102         |

| Ref | erences                                                           | 103         |

| AN  | NEX A                                                             |             |

| AN  | NEX B: Conferences                                                | 112         |

# **Figures list**

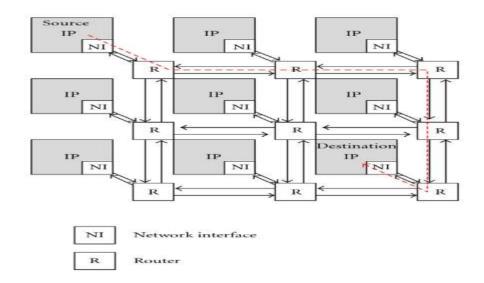

| Figure 1.1: Network on Chip 2D-Mesh architecture             | 4  |

|--------------------------------------------------------------|----|

| Figure 1.2: NoC Layered Communication                        |    |

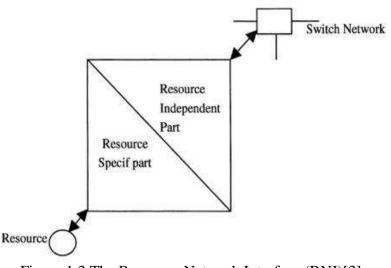

| Figure 1.3 : The Resource-Network Interface (RNI)            |    |

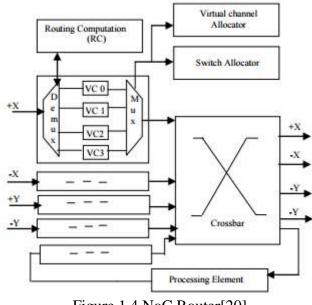

| Figure 1.4 : NoC Router                                      | 13 |

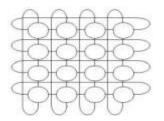

| Figure 1.5: Mesh Topology                                    | 17 |

| Figure 1.6:Torus Topology                                    |    |

| Figure 1.7: Ring topology                                    |    |

| Figure 1.8: Star Topology                                    |    |

| Figure 1.9 : Binary tree topology                            |    |

| Figure 1.10 : Fat binary tree topology                       |    |

| Figure 1.11 : Butterfly topology                             | 19 |

| Figure 1.12 : Spin topology                                  | 19 |

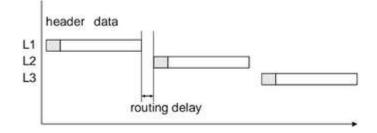

| Figure 1.13: store and forward                               | 21 |

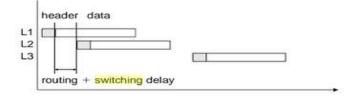

| Figure 1.14: virtual cut-through (VCT) switching             | 21 |

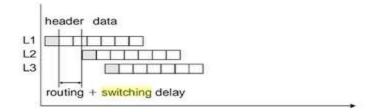

| Figure 1.15:Wormhole switching                               | 22 |

| Figure 1.16:Deadlock                                         | 23 |

| Figure 1.17:Livelock                                         | 24 |

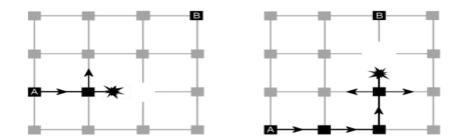

| Figure 1.18:Double Y-channel 2D mesh                         | 27 |

| Figure 1.19: +X sub-network and labeling                     |    |

| Figure 1.20:West-first Routing                               |    |

| Figure 1.21:Negative-first Routing                           |    |

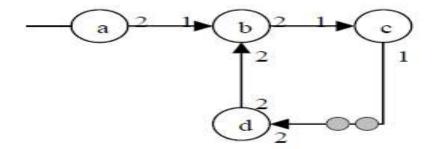

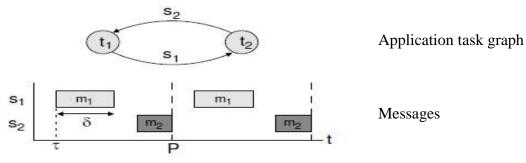

| Figure2.1 Synchronous Data Flow example                      |    |

| Figure2.2 Example application task graph                     |    |

| Figure 2.3: Power reduction techniques classification        |    |

| Figure 3.1: classification of heuristic optimization methods |    |

| Figure 3.2:Polling mechanism for incoming tasks              | 74 |

| Figure 3.3 Interrupt mechanism for incoming tasks            | 75 |

| Figure 4.1: example to random task graph                     | 77 |

| Figure 4.2: Automotive/industrial task graph                 | 79 |

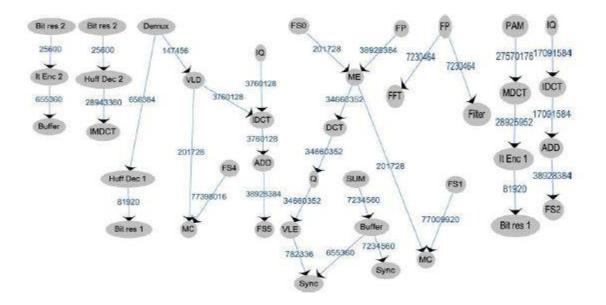

| Figure 4.3: Multimedia system task graph.                    | 79 |

| Figure 4.4:Classical genetic algorithm structure             |    |

| Figure 4.5: example of create chromosome                     |    |

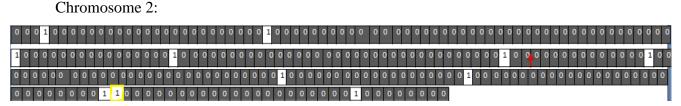

| Figure 4.6: chromosome 2 before crossover                                                | 85      |

|------------------------------------------------------------------------------------------|---------|

| Figure 4.7: chromosome 16 before crossover                                               | 85      |

| Figure 4.8:chromosome 2 after crossover                                                  | 85      |

| Figure 4.9: chromosome 16 after crossover                                                | 85      |

| Figure 4.10: chromosome 2 after mutation                                                 | 86      |

| Figure 4.11: Replacement and verified criterion                                          | 86      |

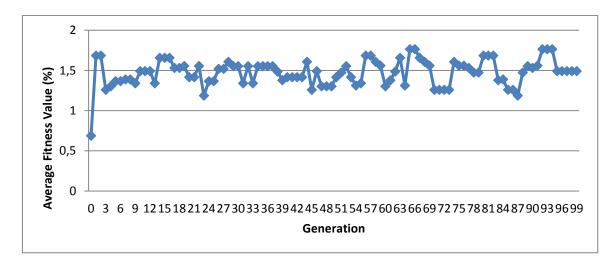

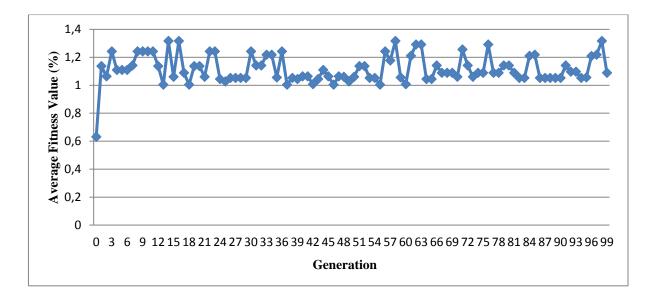

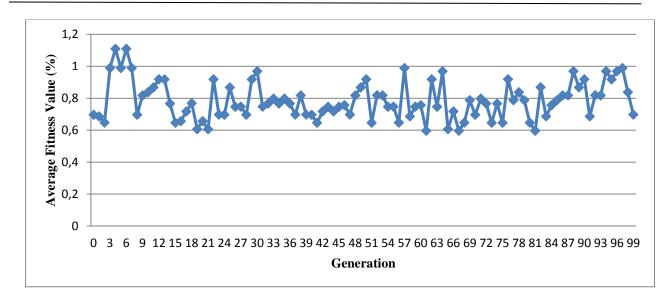

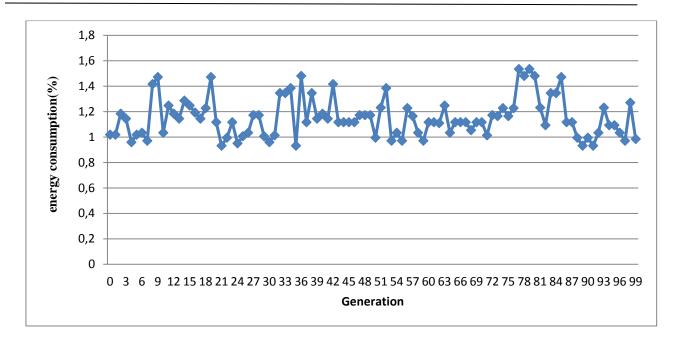

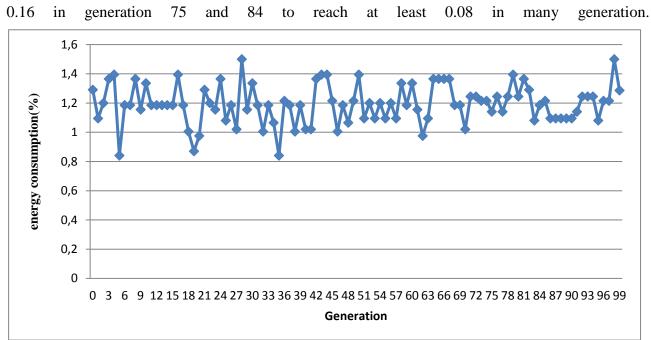

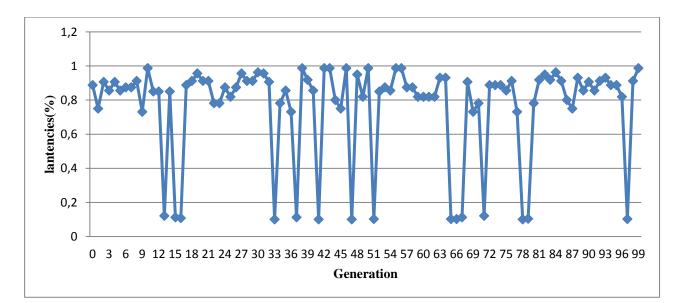

| Figure 4.12: The average fitness value of each generation using GA in MMS                | 88      |

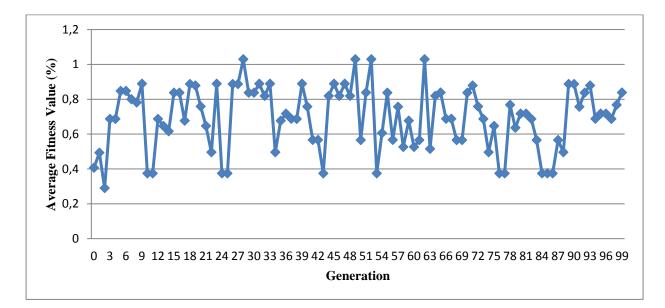

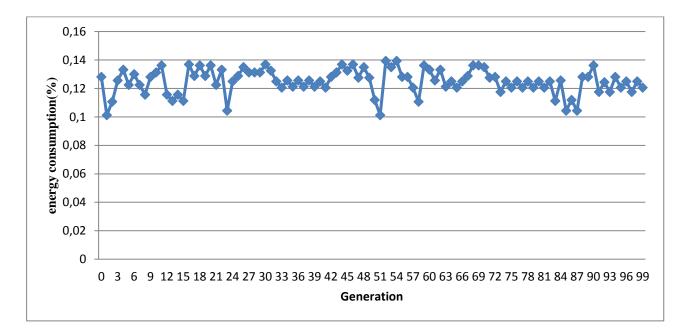

| Figure 4.13: The average fitness value of each generation using GA in auto-indust        | 89      |

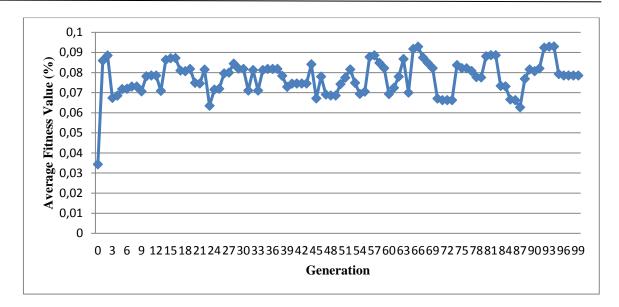

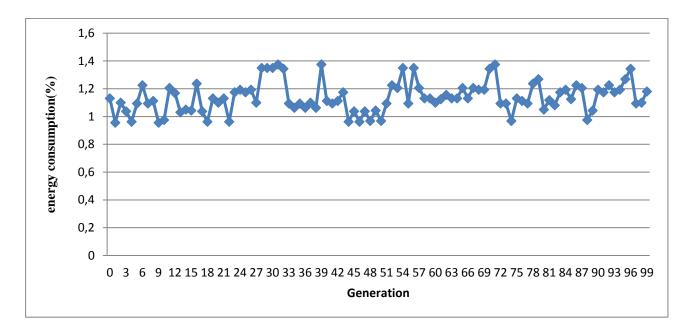

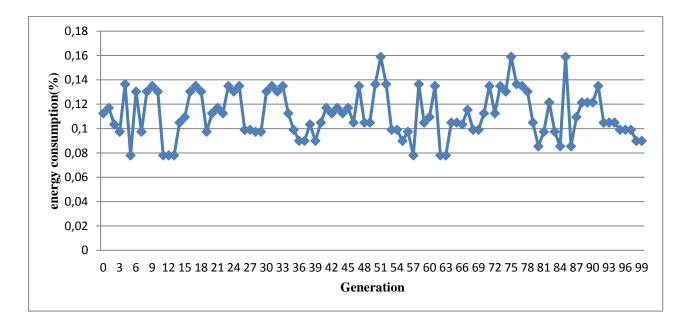

| Figure 4.14: The average fitness value of each generation using GA in random task        | 89      |

| Figure 4.15: The average fitness value of each generation using GAand TS in MMS          | 90      |

| Figure 4.16:The average fitness value of each generation using GA and TS in auto-indust  | 90      |

| Figure 4.17: The average fitness value of each generation using GA and TS in random task | 91      |

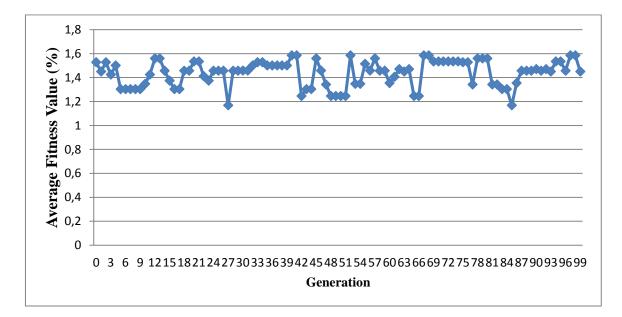

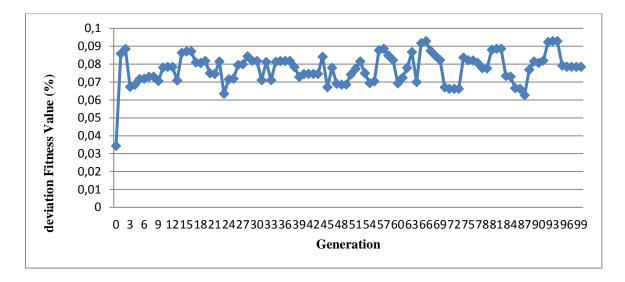

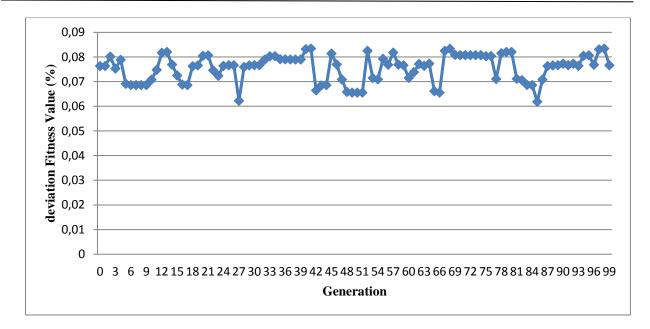

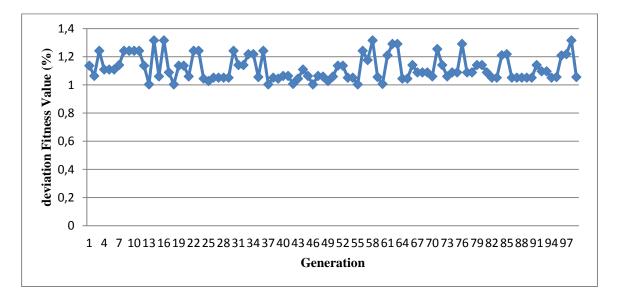

| Figure 4.18:The deviation of each generation using GA in MMS                             | 91      |

| Figure 4.19: The deviation of each generation using GA and TS in MMS                     | 92      |

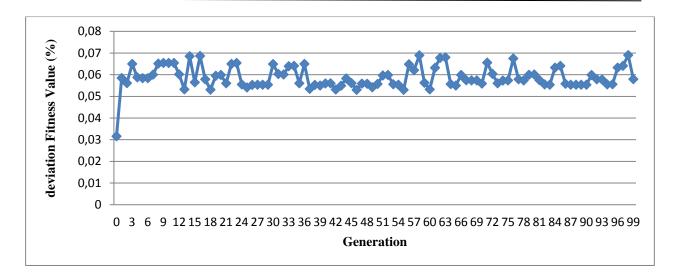

| Figure 4.20:The deviation of each generation using GA in auto-indust                     | 92      |

| Figure 4.21:The deviation of each generation using GA and TS in auto-indust              | 93      |

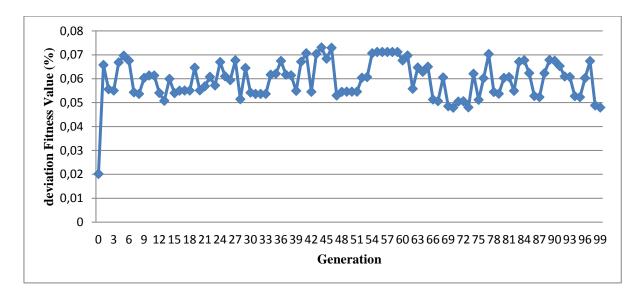

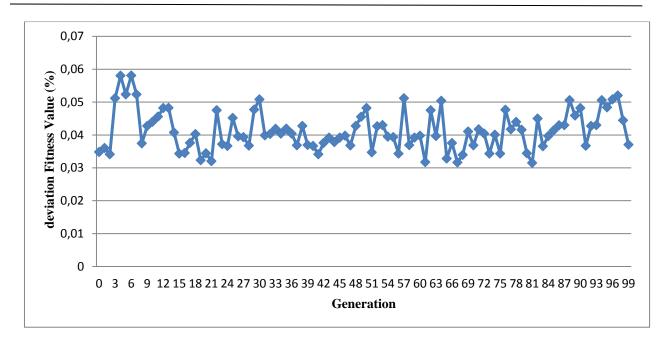

| Figure 4.22: The deviation of each generation using GA in random task                    | 93      |

| Figure 4.23: The deviation of each generation using GA and TS in random task             | 94      |

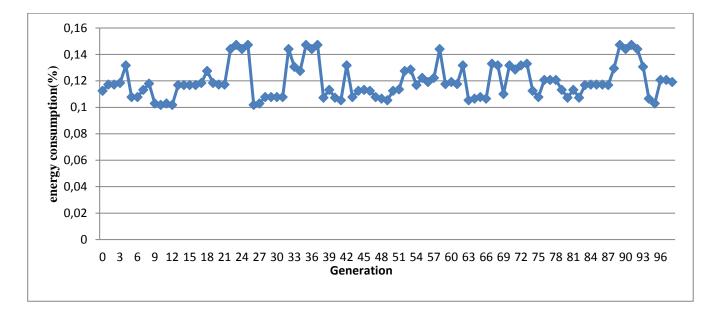

| Figure 4.24: The energy consumption of executing MMS on 5x5 NoC with using task migrat   | ion     |

| in GA and TS                                                                             | 94      |

| Figure 4.25: The energy consumption of executing MMS on 5x5 NoC with using task migrat   | ion     |

| in GA                                                                                    | 95      |

| Figure 4.26:The energy consumption of executing auto-indust on 5x5 NoC with using        |         |

| task migration in GA and TS                                                              | 95      |

| Figure 4.27:The energy consumption of executing auto-indust on 5x5 NoC with using        |         |

| task migration in GA                                                                     | 96      |

| Figure 4.28: The energy consumption of executing random task on 5x5 NoC with using       |         |

| task migration in GA and TS                                                              | 96      |

| Figure 4.29: The energy consumption of executing random task on 5x5 NoC with using       |         |

| task migration in GA                                                                     | 97      |

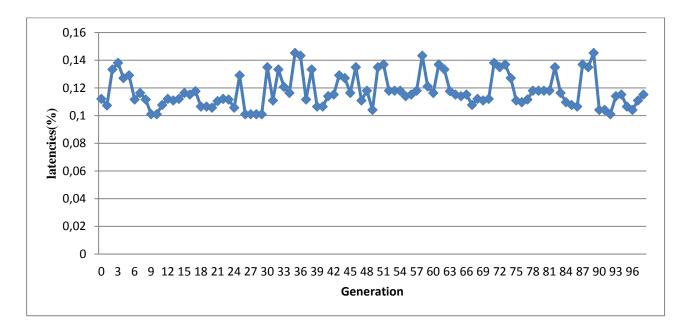

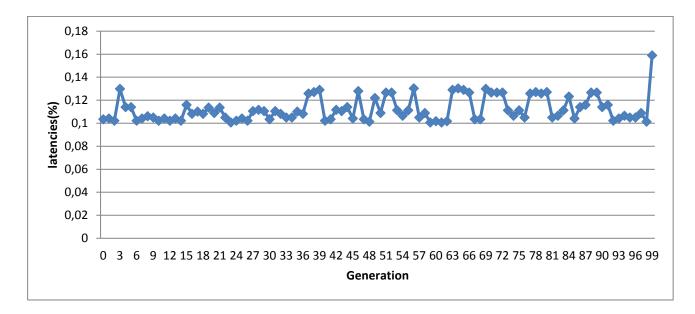

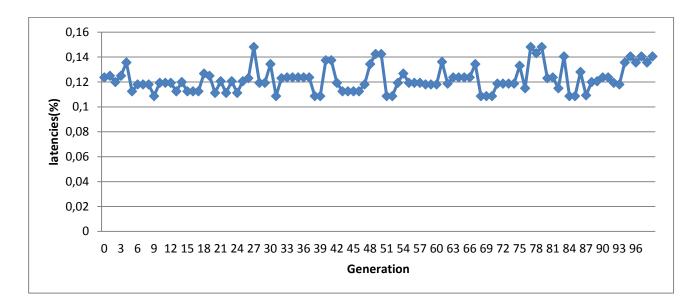

| Figure 4.30: The latencies of executing MMS on 5x5 NoC with using task migration in      |         |

| GA                                                                                       | 97      |

| Figure 4.31: The latencies of executing MMS on 5x5 NoC with using task migration         | n in GA |

| and TS                                                                                      | 98             |

|---------------------------------------------------------------------------------------------|----------------|

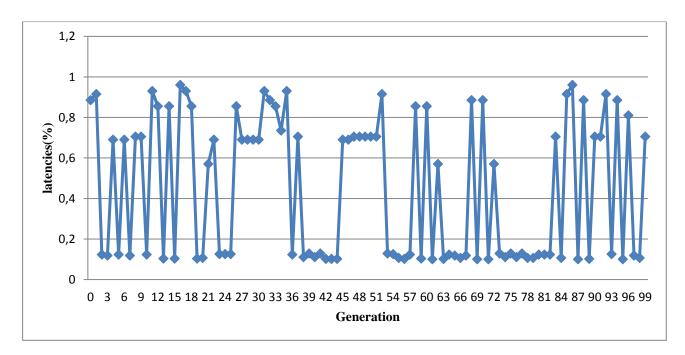

| Figure 4.32: The latencies of executing auto-indust on 5x5 NoC with using task migration    |                |

| in GA and TS                                                                                | <del>)</del> 8 |

| Figure 4.33: The latencies of executing auto-indust on 5x5 NoC with using task migration in |                |

| GA                                                                                          | 99             |

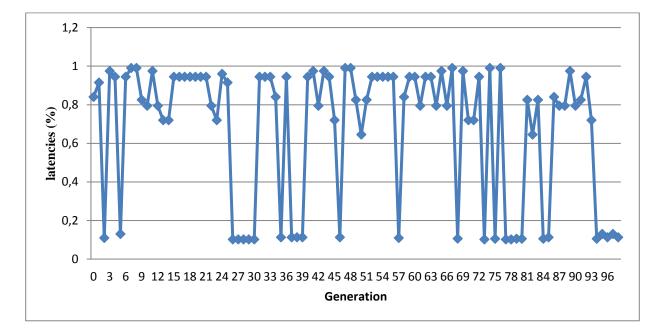

| Figure 4.34: The latencies of executing random task on 5x5 NoC with using task migration in |                |

| GA and TS                                                                                   | 99             |

| Figure 4.35: The latencies of executing random task on 5x5 NoC with using task migration    |                |

| in GA1                                                                                      | 00             |

## Tables list

| Table 1.1: Comparison Of Embedded System Architectures                        | 9   |

|-------------------------------------------------------------------------------|-----|

| Table 2.1: Comparison between different power reduction techniques.           | 53  |

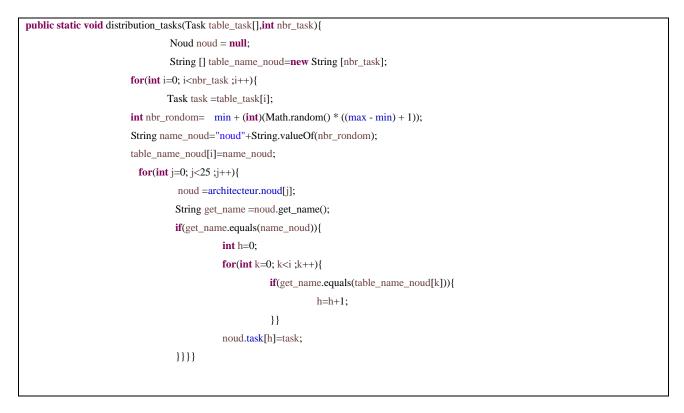

| Table 4.1: Comparison between GA and TS, GA in executing mms2 and auto-indust | 101 |

| Table A.1: Interface of application                                           | 110 |

| Table A.2: code source of distribution_tasks                                  | 110 |

| Table A.3: code source of genetic_algorithem_tabusearch                       | 111 |

# GENERAL INTRODUCTION

#### **1. Problem definition**

Now a days, embedded system is inseparable part of our lives; in home, in office or on our moves (cars, phones, PC, ..), we are always surrounding by embedded system, because it is embedded as a part of a complete device system that includes hardware, such as electrical and mechanical components or a software, such as multimedia applications. A System on Chip (SOC) is a single chip that integrates multiple functionalities that are typically needed for a system into the single chip itself. As the SoC became more complex with the increasing number of low speed, medium speed, and high speed peripherals, this gave way to the design of on-chip interconnect IP required to facilitate effective communication amongst all IO blocks and internal blocks of a SoC, the on-chip interconnect is alternatively termed as Network-on-chip (NoC).

Multimedia applications are real-time systems, consists of tasks and messages between those tasks, The tasks are performed at the level of processors located at the NoC level where each task has a specific execution time defined as a deadline, the task's deadline can be missed with a given threshold in such a way that the quality of streaming multimedia are not degraded, and due to that, a mapping and scheduling algorithms are needed, comes in so that NoC is fair to all, meets their need.

The use of Modern chips in mobile or battery environment has given rise to the requirement of power savings and management. Reduced power consumption means higher battery life, and low execution time means faster performance. But, the problem of the increasing of the number of cores on a single chip leads to the issue of energy consumption and latencies so that number of nodes will be augmented as well, and the time of transmission throw the links will be bigger. Therefore, the power and time management are key issue towards the optimization of the performances in NoC. Task migration is process that describe the movement of an executing task from one host processor (source) in distributed computing system to another (destination), in which processors contain a set of tasks and each task waits for its activation time for execution, so it may take a great time and effort of the processor to perform all tasks that are assigned to it. The process of transferring tasks from one processor to another is used to reduce the pressure on processors (the occupation rate) and reduce the time and power of execution tasks in such a way that the migration overheads won't affect the overall NoC' performances.

However, many heuristic algorithms are designed to find a near optimal mapping such as stochastic global search technique that produce high quality solution, for that, the based bio-inspired methods have been used to solve scheduling and mapping problems such as genetic algorithms, The genetic algorithms' performance is largely influenced by crossover and mutation operators, the probabilities of applying those operators can be controlled by tabu search technique.

#### 2. Contributions

The genetic algorithm examines complex problems by developing a range of possibilities for possible solutions to these problems. Therefore, in our work, we will use it in order to optimize the NoC performances such as energy consumption under timing constraints with the combination of tabu search. Also, we will exploit the approach of migrating tasks from a current processor to another, under certain constraints that lead to improve the performances and minimize the migration overheads.

The process of the algorithms is divided into several stages, the most important is the selection and experimentation phase, which have the role to choose the position of tasks at the processors level and then to take the decision of transfer possibility or not, in which means, the decision of migrating the current task or not. The possibility of the transfer depends on some criterion that should be available on the destination node, those criterions represent the needs of the migrated task such as; the sufficient buffer space to store the incoming migrated data or the availability of the channels to transfer those data. The two processors are chosen in terms of the processor, Faster and less effort.

The tabu search is applying on chromosomes in both; selection phase or population phase (the creation of the first population), and each chromosome will be tested. If this chromosome increases power consumption and latency (ruin the improving of fitness function values), it will be placed in the search table to be avoided in each selection of the future generations. This means that whenever

we choose a chromosome before the experiment, we go to the search table to make sure that it is not in the search table.

In NoC, some processors have a large number of tasks to execute, while others find some idle (no execution task). Therefore, these tasks bring migration to these processors to reduce pressure on them. On the other hand, there are tasks that cannot be performed until assigning them to an executable from another task. This may take time to reach, so it's time to leave it next to it to save execution time. However, this process must be routed. These tasks cannot be allowed to move randomly. Genetic solutions provide migration and an optimal schedule that includes solutions that cannot contribute to facilitating the migration process.

#### 3. Thesis Overview

The thesis is organized as follows:

In chapter1, a description of the concepts and the main parts in the field on network on chip will be done. We will first define the embedded system with its different architecture; and then we will give an introduction of the basic concepts.

In chapter 2, we will put the light on understanding the model of energy-efficient and delay model of NoC based multimedia application. Also, we will describe the different system level-based power reduction techniques with a state of the art of the researches on the last decade with a comparison between them.

In chapter 3, we will present a state of art of the optimization algorithms that are considered as the most used in literature, and especially those based on network on chip.

In chapter 4, we will detail our proposed solution, tests and experiments, with taking as case of study two benchmarks-based multimedia application task graphs: the multimedia system (MMS), the automotive industrial, and random task graph on 2Dmesh 5x5 network on chip.

We will finish this manuscript with a conclusion that summarizes the results obtained from discussing the proposed ideas.

# CHAPTER I

# NETWORK ON CHIP

#### 1. Introduction

Network on Chip (NoC) is a new paradigm that replaces System on Chip (SoC) design. Increasing integration produces a situation where bus structure, which is commonly used in SoC, becomes blocked and increased capacitance poses physical problems. In NOC architecture, traditional bus structure is replaced with a network which is a lot similar to the Internet. Data communications between segments of chip are packetized and transferred through the network. The network consists of wires and routers. Processors, memories and other IP-blocks (Intellectual Property) are connected to routers. A routing algorithm plays a significant role on network's operation. Routers make the routing decisions based on the routing algorithm [104].

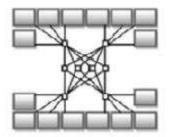

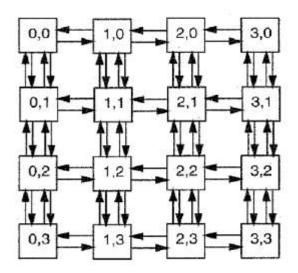

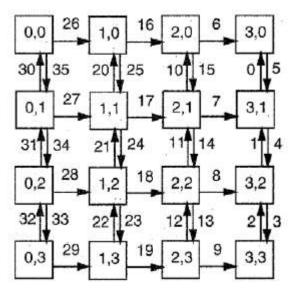

Figure 1.1: Network on Chip 2D-Mesh architecture.[89]

Networks on chip, a new interconnection concept made possible by the evolution of silicon technology, is becoming a preferred solution for simplifying the integration of complex components on systems-on-a-chip. In this chapter we will definite embedded system with a variance between different architectures of embedded system, present à different routing algorithm of NOC, the different main component and the layer communication of NOC

### 2. Embedded System

### 2.1 Embedded System Definition

There are many definition of embedded system ,we mention:

- An embedded system is a system that has software embedded into computer-hardware, which makes a system dedicated for an application (s) or specific part of an application or product or part of a larger system.

- An embedded system is one that has a dedicated purpose software embedded in a computer hardware.

- It is a dedicated computer-based system for an application(s) or product. It may be an independent system or a part of large system. Its software usually embeds into a ROM (Read Only Memory) or Flash.

- It is any device that includes a programmable computer but it is not itself intended to be a general-purpose computer.

- Embedded Systems are the electronic systems that contain a microprocessor or a microcontroller, but we do not think of them as computers

— the computer is hidden or embedded in the system [82].

### 2.2 Real-Time System:

#### 2.2.1 Real-Time Scheduling Techniques:

2.2.1.1 Rate Mono tonic (RM):

The concept of RM was firstly introduced by the authors in [17], and it was one of the first scheduling policies developed for real-time systems and it is still very widely used. We say that

RMS is a **static scheduling policy** because it assigns fixed priorities to processes. It turns out that these fixed priorities are sufficient to efficiently schedule the processes in many situations.

The theory underlying RMS is known as **rate-monotonic analysis** (**RMA**). This theory, as summarized below, uses a relatively simple model of the system.

- All processes run periodically on a single CPU

- Context switching time is ignored.

- There are no data dependencies between processes.

- The execution time for a process is constant.

- All deadlines are at the ends of their periods.

- The highest-priority ready process is always selected for execution.

The major result of rate-monotonic analysis is that a relatively simple scheduling policy is optimal. Priorities are assigned by rank order of period, with the process with the shortest period being assigned the highest priority. This fixed-priority scheduling policy is the optimum assignment of static priorities to processes, in that, it provides the highest CPU utilization while ensuring that all processes meet their deadlines. [13]

Rate-monotonic scheduling is a static priority-based mechanism [17]. Priorities assigned to processes are inversely proportional to the length of the period. That is, the process with the shortest period is assigned the highest priority. Processes are executed in preemptive manner; at any time, the highest priority process with outstanding computation requirement is executed.

Amongst all the class of static priority scheduling schemes, it has been shown that rate monotonic priority assignment is optimal [17]. This implies that, if a given static priority scheduling algorithm can schedule a process system, the rate-monotonic algorithm is also able to schedule that process system. In the case of the rate-monotonic scheduling algorithm, optimality implies the imposition of constraints upon the process system and it includes the following characteristics:

- Fixedset of processes.

- All processes are periodic.

- All processes have deadline equal to period.

- One instance of a process must be complete before subsequent instances are run.

- All processes have known worst-case execution times.

- No synchronization is permitted between processes.

- All processes have an initial release at time 0.[71]

2.2.1.2 Deadlock Monotonic (DM):

DM is an optimal dynamic priority scheduling technique that assigns to each task a priority based on the shorter task. During execution the scheduling order privilege the task with the earliest deadline. Real-time system is schedulable under EDF if and only if

$$\sum U_i \le 1$$

Where  $U_i$  is the processor occupancy by the task i

However, the rate monotonic scheduling technique has a simpler implementation, even on systems without explicit support for timing constraints (periods, deadlines), and offers a best predictability for the highest priority tasks whereas earliest deadline first is a full processor utilization with misbehavior during overload conditions.

#### 2.3 Embedded System Different Architectures

#### 2.3.1 System on Chip (SoC):

System on Chip is a new form of embedded system, which integrates microprocessor, analog IP cores, digital IP core and memory (or off-chip memory controller interface) on a single chip. It is usually customized (CSIC) or a standard product for particular purposes (ASSP). It successfully integrate the hardware integrated circuits and embedded software, which can implement the computer system functions, on a silicon chip, and it belongs to the emerging cross-disciplinary for computer and microelectronics Soc represents a new generation of technology development of embedded processor, its design technology provides an opportunity for computer professionals to be involved in IC design area. And SOC design is still hot now in application design and other areas like microelectronics technology. [67]

#### 2.3.2 Multiprocessor System-On-Chip (MPSOC):

The multiprocessor system-on-chip uses multiple CPUs along with other hardware subsystems to implement a system. A wide range of MPSOC architectures have been developed over the past decade. This paper surveys the history of MPSOCs to argue that they represent an important and distinct category of computer architecture. We consider some of the technological trends that have driven the design of MPSOCs. We also survey computer-aided design problems relevant to the design of MPSOCs.[109]

### 2.3.3 NoC:

Network-on-chip is an emerging alternative that overcomes the above-mentioned bottlenecks for integrating a large number of cores on a single SOC. NOC is a specific flavor of interconnection networks where the cores communicate with each other using a router-based packet-switched network [89].

### 2.3.4 Comparison of Embedded System Architectures:

|     | PROS                                                                                                                                                                                                                                                                                                                 | CONS                                                                                                                                                                                                                                                                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOC | <ul> <li>-An SoC consumes less power.</li> <li>-A smaller size means it is lightweight and of small size.</li> <li>- the cost of an SoC is small due to advancements in VLSI technology.</li> <li>-As mentioned in the first point, cabling is not much required and so the cost of cabling is conserved.</li> </ul> | CONS -Initial cost of design and development is very<br>high Even a single transistor or system damage<br>may prove to be very costly as the complete<br>board has to be replaced, and its servicing is<br>very expensiveIntegrating all systems on single chip<br>increases complexityIt is not suitable for power-intensive |

|     | -An SoC provides greater design security<br>at hardware and firmware levels.                                                                                                                                                                                                                                         | -It is not suitable for power-intensive applications.                                                                                                                                                                                                                                                                         |

|     | -An SoC provides faster execution due to high speed processor and memory.                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                               |

| MPSOC | <ul> <li>-MPSOC provide enoumous computational capacity in an energy efficient and cost efficient way.</li> <li>-computational performance.</li> <li>-reduction of physical units.</li> </ul>                                                                                                                                                                         | <ul> <li>-MPSOC architectures were not designed<br/>with storing focuson safety and certification</li> <li>-MPSOC have serious drawbacks and<br/>limitation with respect to domain</li> <li>- Lacking of temporal determinism.</li> </ul>                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | -heterogeneity.                                                                                                                                                                                                                                                                                                                                                       | - Error propagation and non-intended interference.                                                                                                                                                                                                                                                                                |

| NOC   | <ul> <li>Only point-to-point one-way wires are<br/>used for all network</li> <li>sizes, thus local performance is not<br/>degraded when scaling.</li> <li>Routing decisions are distributed.</li> <li>The same router may be re-instantiated<br/>for all network sizes</li> <li>(communication reusability).</li> <li>Aggregated bandwidth scales with the</li> </ul> | <ul> <li>Internal network contention may cause large latencies.</li> <li>Bus-oriented, IPs need smart wrappers.</li> <li>Software needs clean synchronization in multiprocessor</li> <li>systems.</li> <li>System designers need re-education for new concepts.</li> <li>it is mush more costly to produce than a bus-</li> </ul> |

|       | network size.                                                                                                                                                                                                                                                                                                                                                         | based system due to the large overhead of area and the power consumption of router                                                                                                                                                                                                                                                |

Table 1.1: Comparison Of Embedded System Architectures

### 3. NoC Main Components

### 3.1 NoC Layered Communication

Network-On-Chip uses a layered communication approach, similar to the OSI model which is at the foundation of LANs and WAN, but it is simpler and not all layers are included. Thus, in NoC, mostly three layers are considered (i.e. physical data link and network layer).

| Node        |                                 | Node        |

|-------------|---------------------------------|-------------|

| Application | Router                          | Application |

| Transport   |                                 | Transport   |

| Network     | Network<br>Datalink<br>Physical | Network     |

| Datalink    |                                 | Datalink    |

| Physical    |                                 | Physical    |

Figure 1.2: NoC Layered Communication

#### 3.1.1 The Network Layer:

Switches are implemented in this layer. This layer hangs in charge also the topology of the network. Since addressing is strongly related to the topology, it is also treated in this layer. It defines the routing technique used for routing packets across the network and topology. It therefore routes packets from source to destination, resource addressing and packet buffering. It is also responsible for providing quality of service by addressing issues of latency, throughput, and jitter, etc. The Protocol Data Unit (PDU), which is the set of information exchanged between levels in the OSI system, used for communication between the entities of this layer is called a packet.[3]

#### 3.1.2 The Data Link Layer:

It defines the bit exchange protocol on the links between the routers (eg, handle of hands, emission credit, etc.). It is therefore concerned with flitisation / package node to node communication, detection and correction of transmission error (bit of parity), flow control, schema encoding, etc. This layer ideally transmits data from one point to another, it could be omitted in a simulation. The omission is under the assumption that all data is transmitted without errors. Detection and Correction of the physical layer are implemented in the data link layer.[3]

#### **3.1.3** The physical layer:

This is the lowest level layer of a NoC, it processes the actual data transfer. She is responsible for the clock signals for each connection, the number and nature of interconnection, control signals, electrical levels, the physical means by which will be transported the packets, as well as the way the data is transported (width of words carried in number of bits), etc. As this layer deals with electrical properties, simulation is best done in an analog simulator like Spice [81]. Most of them of the six layers described above, the smallest unit of time is a clock cycle. However, when simulating the physical layer, the time should be expressed in time physical. Co-simulation with physical time and clock cycles would be difficult to implement and expensive in calculation. [3]

#### **3.2 NoC Main Components:**

There are three main types of components, namely routers / switches, Nodes also known as Intellectual Property (IP), and Resource Network Interfaces:

#### 3.2.1 Node:

A node represents an element of the SoC that communicates with other elements; it can be a cluster of nodes when the NoC is used as a global interconnect or a simple element such as: a general-purpose processor, a DSP (Digital Signal Processor), which is a microprocessor optimized for executing digital processing applications. the signal (filtering, signal extraction, etc.) as quickly as possible, a memory, a specific application hardware component, I / O controller, graphics controller, the mixed signal module, the unit radio frequency (RF) etc. Node should be implemented using the same technology as the network switch[12]. The designer can build own node or reuse commercial resources available from different component vendors.[3]

#### 3.2.2 The Resource-Network Interface (RNI):

The RNI links a node to a network router. Therefore, it allows the node to send data to the router. The role of RNI in NOCs is the same as of the network card for the Internet [12]. The RNI consists of two parts, the dependent part resources and the independent portion of resources as shown in Figure 1.3. The part resource-independent is designed so that the RNI appears as another router connected to the router. The design of the independent part of the resources is common to all resources. If homogeneous PEs are used then the dependent part of resources can be reused and it will be the same for all resources, otherwise it is different for each resource.

The dependent part of the resources is responsible for the flitisation / deflitisation and the implementation of the encoding scheme. In the case of source routing, the RNT also contains routing tables and she is responsible for adding the full path in the header flit.[3]

Figure 1.3 The Resource-Network Interface (RNI)[3]

#### 3.2.3 Router:

Routers constitute the most important element in the "NoC" architecture. They allow the implementation of the routing strategy and the flow control algorithm. Additionally, the routers contain buffers to save coming packets. The routing algorithm implemented in the routers determinate destination of each entering packet. It usually implements simple minimal-path functions. [64]

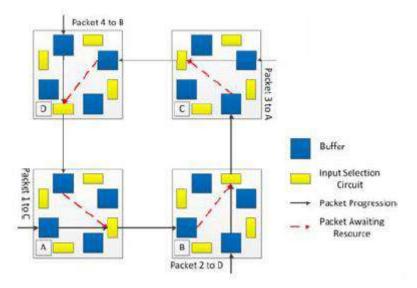

Router also called switch. These components are in charge of forwarding data to the next tail. On the routers we can find implemented the routing protocol, buffer capabilities and the switching method. In general, the router component is composed of the next elements: Arbitrer, which its main task is to grant channels (selecting an input port and an output port) and route packets; Crossbar, of n input x n output ports that direct the input packet to the corresponding output port; and buffer or queue, if that is the case – as it is in the packet switching protocols – which is used to buffer incoming and outgoing data in the router. [28]

A NoC router is implemented using wormhole technique it consists of buffers, switches, and control units which are required to store and forward flits from the input ports to the desired output ports. The architecture is actually similar to that of modern routers, but with smaller area and buffer size .figure 1.4 shows a NoC 16 buffer slots per input port. The buffer slots are divided into four queues, and each queue is called a virtual channel (VC) [76]. There are four cardinal input ports and output ports connected from and to +x, -x, +y and -y directions. The last pair of input/output ports is connected from and to the processing element (PE). The four VCs are sandwiched between the demultiplexer connected to the input port, and the multiplexer connected to the crossbar. Each input

unit can communicate with router, virtual-channel allocator, and switch allocator, which are responsible for Routing Computation (RC), Virtual-Channel Allocation (VA), and Switch Allocation (SA), respectively. The crossbar is controlled by the switch allocator for correctly connecting input ports to output ports. [20]

Figure 1.4 NoC Router[20]

#### 3.2.4 The links:

Links are logical connections between two (or more) communicating elements [64] [76][6]. They allow point-to-point connections between IPs resources and RNI s network-resource interfaces, between RNI and routers and between routers. They are the ones that offer bandwidth and carry information between communicating elements.

A link can consist of several virtual channels, there are three types of links that are defined by the direction of the transmissions. They can be unidirectional in input, unidirectional inoutput or bidirectional (input / output).

In electronic component manufacturing technologies (CMOS: Complementary Metal Oxide Semiconductor), the channels are implanted as global signals of the circuit. Therefore, although reduced, the problems of delays and dispersion of Signals may also exist in NoCs. In order to solve these problems, the signals are commonly segmented by repeaters, usually buffers, which allow

restore the level of the tension of the files. Since the queues have a significant length, repeaters can incorporate registers to pipeline the data transmission. So, these come at a rate that coincides with their use by the calculation elements connected to the network [14][3].

#### **3.3 Flow control:**

The control logic can be used for tasks such as error detection / correction or flow control. In order to ensure that the packets reaches its specified destination and without errors or loss it must control the flow. In the following, we will define the most affecting flow control in NoC.

#### **3.3.1** The delay of the packets:

In order not to be forced to destroy conflicting packets, they can be delayed in queues. However, in the majority of NoCs, the surface consumed by a router comes from the place taken by these files. Therefore, a compromise must be found during the design of the router to minimize the area used by the queues without degrading the required performance.[1][3]

#### a. The size of queues:

The size includes the width of the queues in number of bits and their depth defining the number of words that can be stored. The first parameter that directly affects the size of the queues is the chosen switching mode [18][3]. Indeed, the files may contain several packets, a single packet or a part of the packet. Regarding the width of the queue, it can not be smaller than that of a flow control unit (flit). In addition, the size must be rigorously determined because it can affect the maximum clock frequency and the cost in terms of area and power consumption of the routers. Finally, an inappropriate size may imply congestions within the network with a reduction in bandwidth useful. Queues can be placed at different positions in the router: input, output, or virtual output [2][3].

#### b. The position of the queues:

We distinguish three type of queues, and they are defined as follows:

**i. Input queues:** in this first case, each input port of the router has a queue. Although this technique is the least expensive on the surface, it can induce saturation due to head-of-line blocking. This happens when data at the top of the queue can not access the associated output port, blocking other packets in the queue, even if their output is free.

**ii. Output queues:** When the queues are positioned at the output of the router, each output port has as many queues as there are ports of entry. This technique offers better performance than the previous one but the surface is necessarily more important.

**iii.** Queues in virtual output or virtual channels: The idea of queues in virtual output is to combine the advantages of both techniques preceding. Thus, each port of entry has several queues to distribute the packets according to their destination or priority. We are talking about virtual channels because for a single physical channel, there will be as many virtual channels as there are queues waiting [1] [52][3].

Although they involve an increase in surface area and latency, because of the memory and control, virtual channels have several advantages:

- they avoid deadlocks (blocked packets are stored in different channels virtual ones to let other packets pass);

- they optimize the use of links;

- they increase network performance (improved latency and bandwidth);

- they provide separate services (through separate traffic and priority levels different)[3]

#### **3.3.2** The switching matrix:

The router's input and output ports are all connected to each other through the switching matrix [38]. It can be implemented by a crossbar or by cascading several stages of multiplexers because the matrix has the role of multiplexing the input data of the router to its output ports [1][3].

#### 3.3.3 Arbitration:

When within a router, at least two packets wish to exit through the same port and this, at the same time, an arbitration must be done in order to choose the one that will come out first. Even though, there are different techniques for arbitrating conflicting packets, the most commonality is impartiality. Indeed, the arbitrator must be able to provide equitable access to output ports if the packets have the same priority [1][3].

The main arbitration policies that can be found in the NoCs are Access Time-Division Multiple Access (TDMA), reservation of Time-slot, Turnstile or Round-robin, and fixed priority [25][3].

**i.** By TDMA: it is a mode of multiplexing consisting of dividing the time into periods short called time-slots, and to be assigned to each element communicating one or more beaches. Thus, for the duration of a beach, the shared resource will be fully reserved for the element to which the time-slot is associated. However, the time range must be carefully aligned with the risk of introducing additional latencies [25][3].

**ii. By time-slot reservation:** the time-slot reservation policy is actually a TDMA type policy in which the reservation of the time range is repeated periodically.

**iii. By tourniquet or round-robin:** round-robin or round-robin type arbitration represents the most impartial arbitration policy. Indeed, at each cycle, it gives access to a packet from a different input.

**iiii. By fixed priority:** in the fixed priority technique, each packet has a priority fixed by the issuer before entering the network. This priority is used to route the packet from the source to the destination. [3]

#### **3.4 NoC Main Characteristics:**

Performance of NoC depends on various factors such as network topology, routing strategy and switching technique, and each one should be taken in account during the implementation of NoC.

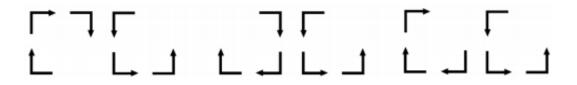

#### 3.4.1 Topology: